# Particle swarm optimization based CMOS low noise amplifier design

Is

Roohollah\_Nakhaei<sup>1</sup>, Seraj.D. Katebi<sup>2</sup>, Alireza Mallahzadeh<sup>3</sup>

[slamic Azad University, Bushehr Branch; Email: r.nakhaei@gmail.com

<sup>2</sup>Shiraz university; Email: katebi@shirazu.ac.ir

<sup>3</sup>Persian Gulf University of Bushehr; Email: mallahzad@pgu.ac.ir

Paper Reference Number: 0101-657

Name of the Presenter: Roohollah Nakhaei

In this paper we propose a particle swarm optimization based approach for designing CMOS low noise amplifier (LNA). Existence of tradeoffs between noise, gain, linearity, stability and power consumption in LNA design, forces the designer to accomplish such a long time complicated work to optimize the circuit. So the utilization of a modern optimization is inevitable. In this work the usage of PSO algorithm in LNA circuit design optimization has been investigated. The performance of LNA circuit is evaluated through HSPICE and PSO algorithm is implemented in MATLAB, so a combination of MATLAB and HSPICE is performed. A cascode LNA is designed using 0.18 mircometer CMOS technology foe near 2.4 GHz band applications. The results of this work indicate the effectiveness of this optimization approach that is a time saver method.

Key words: PSO, LNA, CMOS, Design optimization

## 1. Introduction

Recently, due to emerging commercial wireless application, high-performance RF circuits are required in modern communication. Low noise amplifier (LNA) is one of the most important and essential building blocks in RF transceivers [1]. It is integrated into the receiving chain and is either directly connected to the antenna or placed after RF pass band filter[2], and it should provide a proper low noise amplified signal to the next stage, e.g. mixer, from a week input signal by adding as little inherent as possible[3].

The LNA should provide sufficient tranceconductance gain with acceptable linearity and power consumption to allow for long battery life especially in portable hand-held applications. Therefore there are some tradeoffs between gain, noise figure (NF), linearity and stability in LNA design optimization [4].

In order to achieve the best performance of the designed circuit, designers must continuously and repeatedly tune the designed circuit elements and perform a circuit simulation using an electric computer-aided design (ECAD) software, to optimize active devices model parameters and sizes, passive devices parameters, biasing conditions, etc. it is in general a long time, high complexity and complicated work. A proper optimization method can be used to overcome this problem.

In this work we implement a particle swarm optimization (PSO) algorithm in MATLAB [5] which has been linked with an electrical simulator, HSPICE [6]. The performance of LNA is considered in terms of NF, IIP3, gain, s-parameters and power consumption.

Price and other market requirements force RF receivers to be integrated in standard CMOS technology along with the rest of digital signal processing unit [7]. Since several applications have been developed near the 2.4 GHz band, such as IEEE802.15.4, IEEE802.11b and Bluetooth, we have simulated a 2.4 GHz CMOS LNA using TSMC parameters for 0.18 µm mixed signal and BSIM30 version 3.1[8].

This paper is organized as follows: The particle swarm optimization concept is explained in Section 2. In Section 3 the LNA design specifications and consideration has been described. We propose the method of optimizing LNA design using PSO in Section 4. The achieved simulation results are discussed in Section 5 and finally, we draw conclusions in section.

# 2. Particle Swarm Optimization

Particle swarm optimization (PSO), first introduced by Kennedy and Ebehart[9], is an evolutionary computation method based on the social behaviour and movement of swarm searching for the optimal and best location in a multidimensional search space and has been found to be robust in solving continues nonlinear optimization problems[10].

This approach simulates the social behaviour of bird flocking or fish schooling model. Each particle (i-th particle) position is represented by a d-dimensional vector and denoted as  $X_i = [x_{i1}, x_{i2}, ..., x_{id}]$  and is randomly initialized. The set of n particle in the swarm are called *population*:  $X=[X_1, X_2,...,X_n]$ . Each particle is assumed to move around in the so called multidimensional space to reach the best position which has the best fitness value. In each iteration of simulation the fitness function is evaluated by taking the current position of each particle, and if achieved fitness value is better than previous best fitness of i-th particle, the current position will be selected as the best previous position of i-th particle and described as PB<sub>i</sub>=[pb<sub>i1</sub>, pb<sub>i2</sub>,..., pb<sub>id</sub>]. The best position among the population is called *global best position* and described as  $GB_i=[gb_1, gb_2, ..., gb_d]$ .

The rate of position change for each particle is called particle velocity:  $V_i = [v_{i1}v_{i2}, \dots, v_{in}]$  $v_{id}$ ], each particle would like to return to its own optimum point, so the velocity has a term proportional to (pb<sub>i</sub>-x<sub>i</sub>), it would like to follow overall best global optimum point too, so a term proportional to  $(gb-x_i)$  is added to velocity. Therefore:  $v_{id}^{k+1} = wv_{id}^{k} + c_1 rand_1^{k} (pb_{id} - x_i^{k}) + c_2 rand_2^{k} (gb_d^{k} - x_{id}^{k})$

$$v_{id}^{k+1} = wv_{id}^{k} + c_1 rand_1^{k} (pb_{id} - x_i^{k}) + c_2 rand_2^{k} (gb_d^{k} - x_{id}^{k})$$

(1)

Where w is intera weight parameter which controls the tradeoff between the global and the local search capabilities of the swarm.  $c_1$  and  $c_2$  are acceleration factors and indicate the relative attraction toward pb and gb respectively. rand<sub>1</sub> and rand<sub>2</sub> are two random numbers uniformly distributed between 0 and 1, which indicate the craziness of particles[10]. k is the iteration number. The new position of i-th particle is then determined by:

$$x_{id}^{k+1} = x_{id}^{k} + v_{id}^{k+1} (2)$$

$x_{id}^{k+l} = x_{id}^{k} + v_{id}^{k+l}$  (2) Generally PSO has the advantage of being very simple in concept, easy to implement and computationally efficient algorithm. Since updates in algorithm consist of simple

adding and multiplication operators and no derivation operation is included, computation time is dramatically decreased compared to other heuristic algorithms. In order to avoid premature Convergence, PSO utilizes a distinctive feature of controlling a balance between global and local exploration of the search space which prevents from being stacked to local minima [11].

# 3. LNA Design Specifications and Considerations

As called previously, there are some tradeoffs between noise figures (NF), gain, linearity and stability in LNA design process. There are some considerations about these design Specifications:

## 3.1 Linearity

Increasing the gain of LNA can degrade the linearity. Linearity of LNA is measured in terms of IIP3 that is required to be maximized. Generally, to achieve higher linearity in RF receivers, IIP3 must be more than -10dBm [12].

#### 3.2 Stability

The stability conditions, if and only if k>1 and  $|\Delta|<1$ , presented by stability factor k must be satisfied [3] where

$$k = (1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|) / (2|S_{21} \times S_{12}|)$$

(3)

$$\Delta = S_{11} \times S_{22} - S_{21} \times S_{12} \tag{4}$$

For CMOS LNAs, the required S21 is normally larger than 10 dB. For S11 and S22, the input/output return losses, less than -10 dB are desirable. Also to avoid unwanted signals to reach the LNA input from the following stages, reverse power gain S12 must be less than -20 dB [12].so in LNA design optimization these specifications must be considered.

# 3.2 Noise

The noise performance of a circuit is typically characterized by a noise factor F or NF which indicates how much degradation occurs in the output signal-to-noise ratio due to the circuit's internal noise [13]:

$$F = \frac{(S/N)_{in}}{(S/N)_{out}} = \frac{total \quad output \quad noise}{total \quad output \quad noise \quad due \quad to \quad source}$$

$$or$$

$$NF = 10 \log \frac{(S/N)_{in}}{(S/N)_{out}}$$

(5)

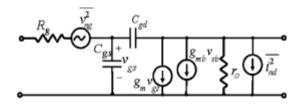

Fig .1 shows the standard CMOS noise model [14]. One of the noise source caused by channel resistance, which is modulated by  $V_{\rm gs}$  its power spectral density given by:

$$\bar{i}_{nd}^{2} = 4kT\gamma g_{do} \quad , \quad g_{do} = \frac{d(i_{d})}{d(V_{DS})}\Big|_{V_{DS}=0}$$

(6)

## Fig 1: Standard CMOS noise model

Which,  $g_{do}$  is the conductance when  $V_{DS}$  is equal to zero.  $\gamma$  is the channel thermal noise coefficient, which depends on channel length and its bias conditions. Finite gate resistance also exhibits the other source of noise. Power spectral density of gate's thermal noise is given by:

$$\overline{v}_{ng}^2 = 4kTR_G \ , \ R_G = \frac{R_g W}{3n^2 L}$$

(7)

Where  $R_g$  is the gate polysilicon sheet resistance, W and L are the width and length of the device and n is the number of gate fingers in the device layout.

Therefore, size and other parameters of active devices and the value of circuit's resistance and bias condition affect the NF and must be optimized in LNA designIf the paper is the result of a research, then the data and material used in the research should be presented here

# 4. Application of PSO to LNA Design

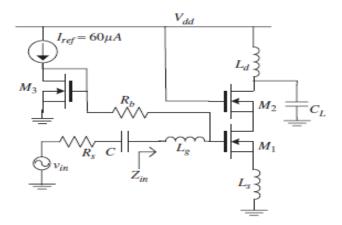

The schematic of LNA under investigation [3] is shown in fig.2. It has the cascode topology with inductive degeneration to provide a high gain and high reverse isolation, which improve the stability and simply input port matching.

Fig.2: The cascade LNA

| The position     | Design specifications                  |  |  |  |

|------------------|----------------------------------------|--|--|--|

| vector's         |                                        |  |  |  |

| elements         |                                        |  |  |  |

| I <sub>ref</sub> | NF                                     |  |  |  |

| $W_{M1}$         | IIP3                                   |  |  |  |

| $W_{M2}$         | Power dissipated                       |  |  |  |

| $W_{M3}$         | S <sub>11</sub> (input return losses)  |  |  |  |

| $L_{d}$          | S <sub>22</sub> (output return losses) |  |  |  |

| $L_{s}$          | S <sub>21</sub> (power gain)           |  |  |  |

| $L_{\rm g}$      | S <sub>12</sub> (reverse power gain)   |  |  |  |

| С     |  |

|-------|--|

| $R_b$ |  |

Table 1. The design parameters and specifications

The purpose of LNA optimization is to achieve the active devices size and passive values that give the best design specifications, which considered in section 3.for this purpose; the PSO algorithm gets a spice netlist of LNA circuit as its inputs. In fact, the particle position vector is the size and value of the active and passive devices. In this work, it is a 9-dimensional vector, as shown in table 1.

Therefore, at first, each particle (i-th particle) selects random values for active and passive devices (or random value for i-th position vector). In each iteration, the algorithm runs the HSPICE for each particle and evaluates a cost function (CF), described in (8):

$$CF = \prod e^{\alpha_i D_i} , \alpha_i \le 1$$

(8)

Which,  $D_i$  s are the design specifications and  $\alpha_i$  s are the importance factors that say which specification has more importance for designer regarding to different especial applications of LNA. Therefore, PB and GB are showing the minimum CF for best previous position and global best position respectively that each particle attempts to reach them.

## 4. Results and Analysis

Considering so called importance factors, three case studies of LNA is carried out using PSO. For each case, achieved value of passive devices and size of active devices and bias current are tabulated in table 2, and a comparison whit three other works is shown in table 3.

|                     | Case   | Case   | Case   |

|---------------------|--------|--------|--------|

|                     | study1 | study2 | study3 |

| $I_{ref}(\mu A)$    | 69     | 142    | 128    |

| $W_{M1}$ ( $\mu$ m) | 111.8  | 94.5   | 109.9  |

| $W_{M2}(\mu m)$     | 700    | 588    | 700    |

| $W_{M3}(\mu m)$     | .2     | 7.5    | 2.5    |

| $L_{d}(nH)$         | 9.17   | 10     | 25     |

| $L_{s}$ (nH)        | .2     | .01    | .07    |

| L <sub>g</sub> (nH) | 15.2   | 16.4   | 13.6   |

| C (pF)              | 284.35 | 305    | 387.35 |

| R <sub>b</sub>      | 200    | 251    | 87     |

Table 2. value and size of devices

In case study 1, the gain has assumed to get much higher priority among other design specifications. As indicated in table 3, the improvement in gain is achieved in cost of linearity degradation and power dissipation. Conversely, the power has more importance for designer, in case study 2. It is clearly visible from table 3 that although the power consumption is decreased but the gain of LNA is decreased too. Finally, considering all

specifications, a reasonable LNA design for general applications is carried out in case study 3, which its gain, s11, s12 and NF are depicted in fig.3.

|                      | Case<br>study1 | Case<br>study2 | Case<br>study3 | Ref[3] | Ref[13] | Ref[15] |

|----------------------|----------------|----------------|----------------|--------|---------|---------|

| technology           | 0.18           | 0.18           | 0.18           | 0.18   | 0.18    | 0.18    |

|                      | μm             | μm             | μm             | μm     | μm      | μm      |

|                      | CMOS           | CMOS           | CMOS           | CMOS   | CMOS    | CMOS    |

| f <sub>0</sub> (GHz) | 2.4            | 2.4            | 2.4            | 2.4    | 5.4     | 2.4     |

| NF (dB)              | 1.5            | 2.1            | 1.06           | 2.15-  | 1.8-2.6 | 2.9     |

|                      |                |                |                | 2.7    |         |         |

| gain                 | 22.15          | 14.17          | 18.9           | 11.2   | 20.5    | -       |

| IIP3                 | -7             | <b>-</b> 3     | -2.3           | -6.5   | -6.2    | -4      |

| (dBm)                |                |                |                |        |         |         |

| $S_{11}$ (dB)        | -15            | -15            | -20.3          | -11    | -18.5   | -10.1   |

| S <sub>12</sub> (dB) | -36.8          | -43            | -44.6          | -60    | -48     | -10.5   |

| power (mW)           | 14             | 2.1            | 3.6            | 2.7    | -       | 11.7    |

Table 3. Results and Comparison

Fig 3: The specifications of case study 3

#### 5. Conclusions

In this paper, a PSO based approach for optimal design of LNA circuit has been reported. Electrical characteristics of the LNA circuit considered in the optimization process are the gain, S parameters, noise figure, power consumption and the input third-order intercept point. The results of this work indicate the effectiveness of this optimization approach that is a time consuming method. We note that this approach can also be applied to design optimization of other circuit and can be embedded into any electronic CAD software which improves the process of design and fabrication.

#### References

- [1] A. Telli, M. Aska(2003) r, CMOS LNA design for LEO space S-band applications, IEEE Can. Conf. Electr. Comput. Eng. 1,(27–30).

- [2] B. Razavi(1998), RF Microelectronics, Prentice Hall Inc.

- [3] S.Toofan et al(2007), A low-power and high-gain fully integrated CMOS LNA, Microelectronics Journal 38 1150–1155

- [4] S.Park, W.Kim(2001), Design of a 1.8GHz low-noise amplifier for RF front-end in a 0.8 mm CMOS technology, IEEETrans .Consum.Electron.47 (1).

- [5] http://www.mathworks.com/products/matlab

- [6] http://www.synopsys.com/products/mixedsignal/hspice/hspice.htm

- [7] J.-H.Tsai, W.-C.Chen, T.-P.Wang, T.-W.Huang, H.Wang(2006), Aminiature Q-band low noise amplifier using 0.13 mm CMOS Technology , IEEE Microwave Wireless Components Lett .16(6)327–329

- [8] <a href="http://www.mosis.com">http://www.mosis.com</a>

- [9] J. Kennedy, R.C. Eberhart(1995), Particle swarm optimization, in: Proc. IEEE International Conference on Neural Networks, pp. 1942–1948.

- [10] J.schneider, S.kirkpatrick(2006), Stochastic optimization , springer-verlag berlin Heidelborg .

- [11] M. Clerc(2002), The particle swarm Explosion, stability and convergence in a multidimensional complex space, IEEE Trans. Evol. Comput. 58–73.

- [12] S. Park, W. Kim(2001), Design of a 1.8GHz low-noise amplifier for RF front-end in a 0.8 mm CMOS Technology, IEEE Trans. Consum. Electron. 47 (1) 10–15.

- [13] S. Toofan et al(2008), Low power and high gain current reuse LNA with modified input matching and inter-stage inductors, Microelectronics Journal 39, 1534–1537.

- [14] D.K. Shaeffer(1997), T.H. Lee, A 1.5-V, 1.5-GHz CMOS low noise amplifier, IEEE J. Solid-State Circuit 32 (5) 745–759

- [15] L.-H. Lu, H.-H. Hsieh, Y.-S. Wang(2005), A compact 2.4/5.2-GHz CMOS dual-band low-noise amplifier, in: IEEE Microwave and Wireless Components Letters, vol. 15, 10, , pp. 685–687.